26.3.11 ZD-EP47 [GPIO] GPIO简介及其工作模式

GPIO,Genaral Purpose Input Output,通用输入输出端口,下面我们将从GPIO特点特性和GPIO的工作模式对GPIO展开介绍。

1 GPIO特点特性

关于特点特性这一块我们就直接照搬一下正点原子的介绍吧,这篇文章主要介绍STM32上GPIO的工作模式。

1.1 GPIO的特点

1,不同型号,IO口数量可能不一样,可通过选型手册快速查询;

2,快速翻转,每次翻转最快只需要两个时钟周期(F1最高速度可以到50Mhz);

3,每个IO口都可以做中断;

4,支持8种工作模式;

1.2 GPIO的电气特性

1,STM32工作电压范围?

$$2V≤VDD≤3.6V$$

2,GPIO识别电压范围?

$$COMS端口: -0.3V \le V_{IL} \le 1.164V $$

$$ \hspace{4.5em} 1.833V \le V_{IH} \le 3.6V$$

3,GPIO输出电流?

$$单个IO最大25mA$$

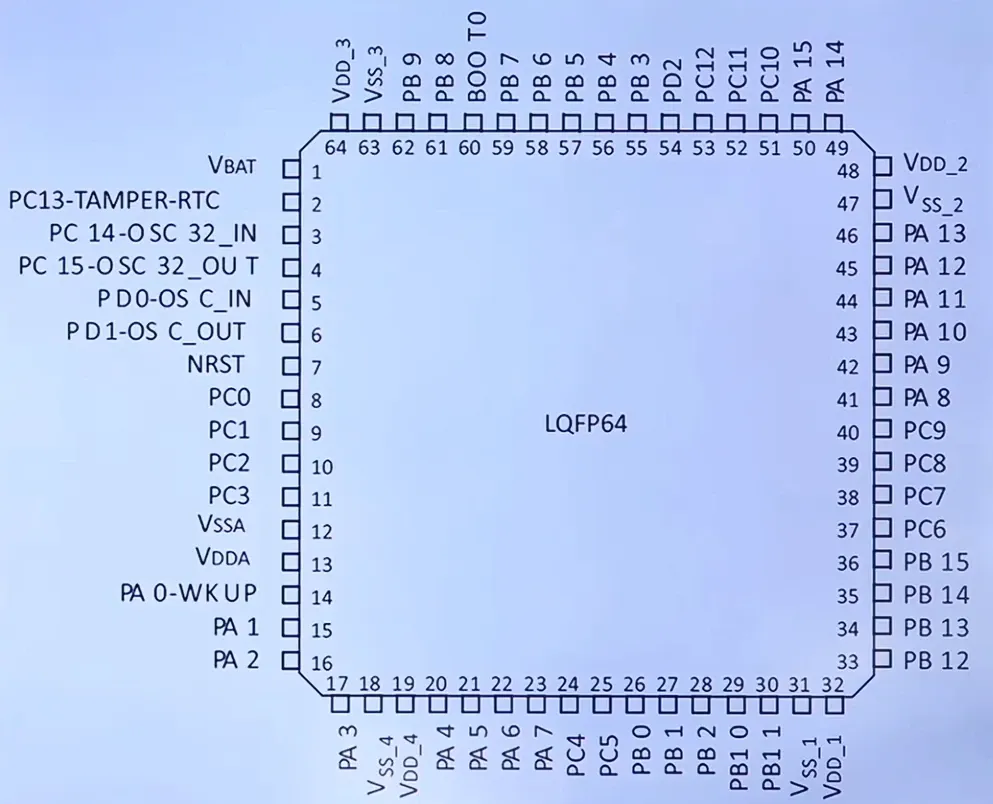

1.3 GPIO引脚分布(以STM32F103xx系列为例)

如图:

共有六类引脚:

- 电源引脚:以 V+角标 命名,如 $V_{DD\_3}$。

- 晶振引脚:以 Pxx-OSCxx_IN/OUT 命名,如 $PD0-OSC\_IN$ ,其中OSC32代表的是低速振荡器,即频率为32.768kHz的振荡器。

- 复位引脚:$NRST$。

- 下载引脚:按照下载方式的不同使用不同的引脚,最常见的SWD下载方式使用到的引脚有 $PA13 , PA14 , V_{SS\_x} , V_{DD\_x}$。

- BOOT引脚:分为 BOOT0 和 BOOT1 引脚,其中 BOOT0 已在引脚上直接标出,而 BOOT1 引脚直接使用 PB2 引脚(不同系列芯片可能有所不同)。

- GPIO引脚:其余以 P 开头的引脚均为GPIO引脚。

GPIO引脚按组区分,如F103xx系列的引脚有GPIOA~GPIOC每组各16个引脚,外加GPIOD的PD0~PD2三个引脚,共有16*3+3=51个GPIO引脚。

2 GPIO的八种工作模式

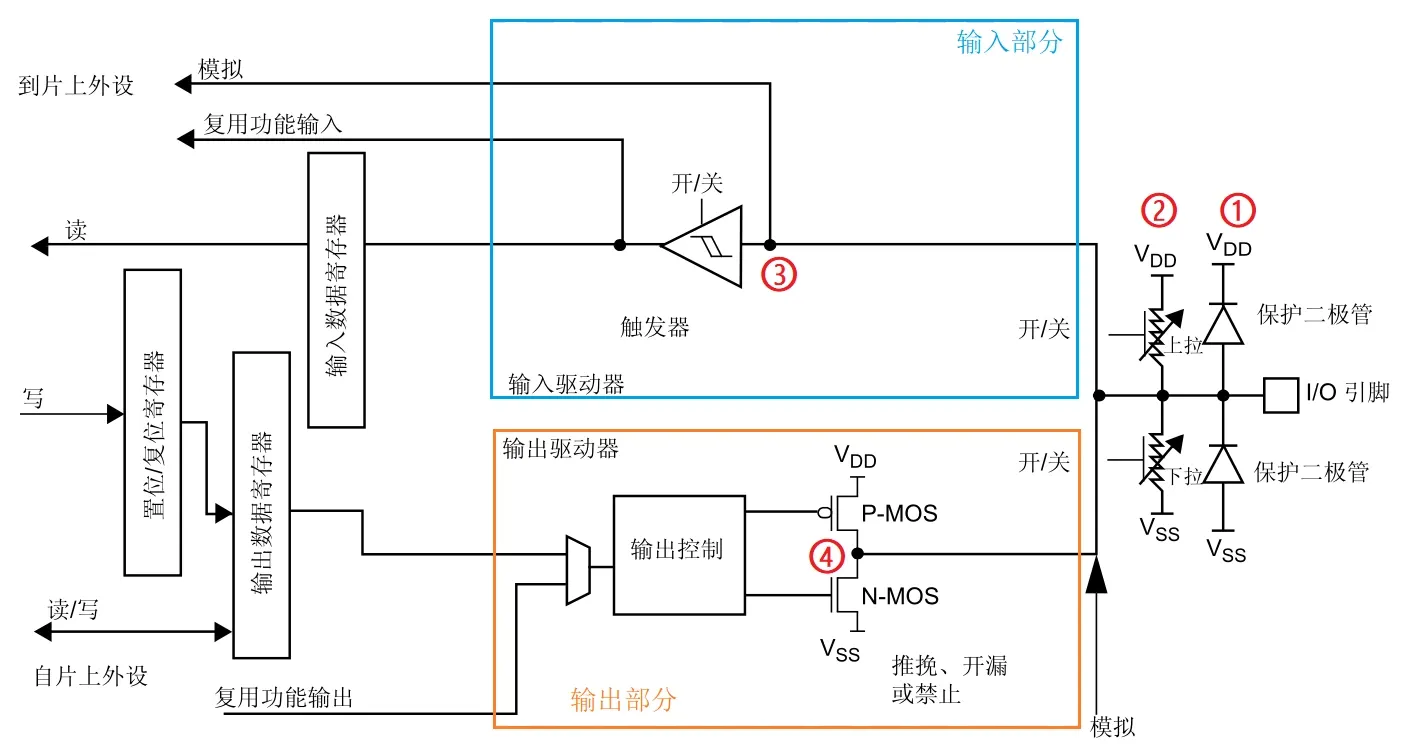

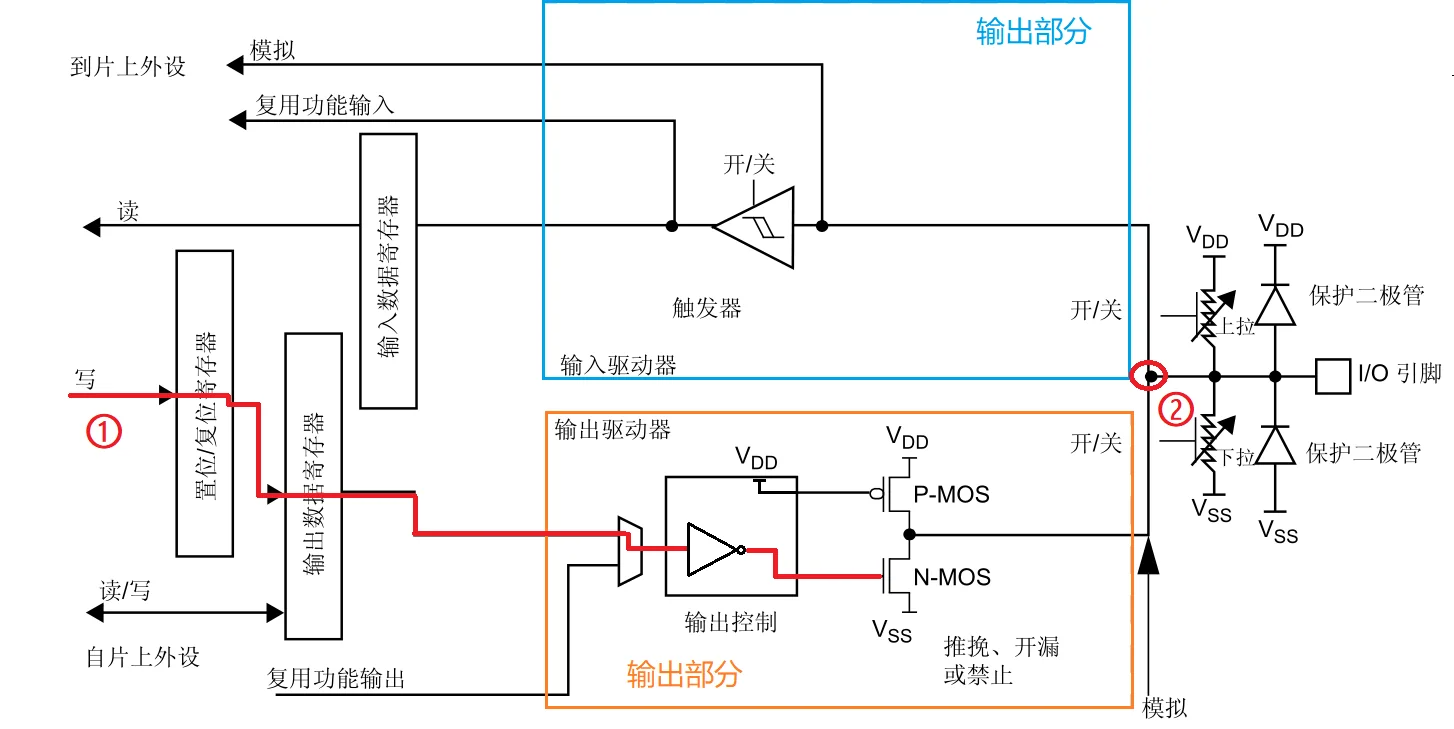

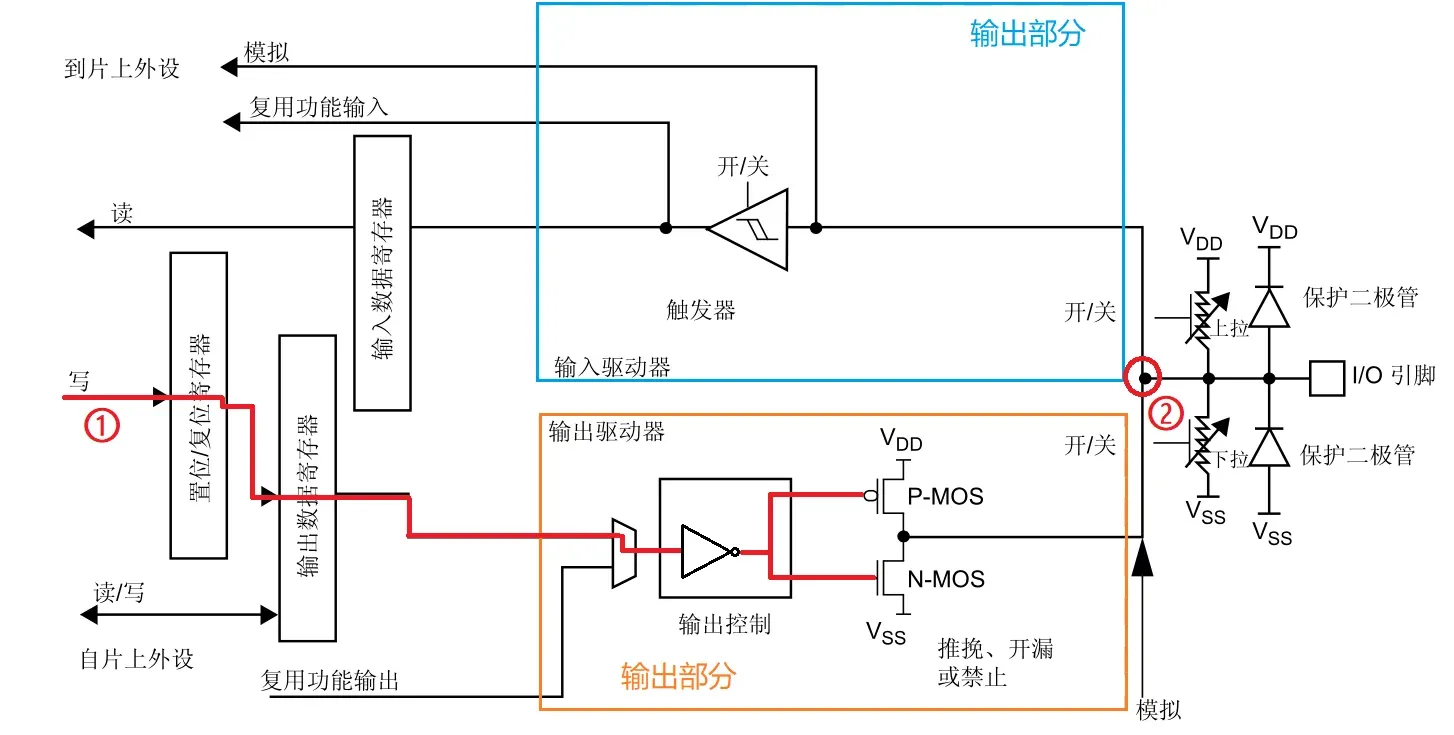

先来看一下GPIO的基本结构。

2.1 GPIO的基本结构

如图所示,除I/O引脚外,其余均为内部结构。内部结构中用于控制工作模式的主要有图中所标的 ①保护二极管 ②上下拉电阻 ③施密特触发器 ④P/N-MOS管,下面分别介绍其作用:

- 保护二极管:用于保护芯片,防止芯片输入过高或过低的电压,但实际效果很弱。其工作方式为当I/O口输入电压略超过3.6V时,与$_{DD}$形成压差,通过上位的二极管的压降(经过二极管的电压一般下降0.3V)作用,使实际输入的电压不超过芯片设计上限的3.6V,同理当I/O输入电压过低(如-5V),经下位接地的二极管的压降作用使得实际输入的电压不低于芯片设计下限的-0.3V,总之其利用的是二极管的钳位电路使得实际输入电压保持在芯片设计范围内,不过其效果有限,当电压过高时可能会击穿二极管导致保护作用失效。

- 上下拉电阻:这边直接引用开发指南的介绍,具体用处会在之后讲到。它们阻值大概在 30~50K 欧之间,可以通过上、下两个对应的开关控制,这两个开关由寄存器控制。当引脚外部的器件没有干扰引脚的电压时,即没有外部的上、下拉电压,引脚的电平由引脚内部上、下拉决定,开启内部上拉电阻工作,引脚电平为高,开启内部下拉电阻工作,则引脚电平为低。同样,如果内部上、下拉电阻都不开启,这种情况就是我们所说的浮空模式。浮空模式下,引脚的电平是不可确定的。引脚的电平可以由外部的上、下拉电平决定。需要注意的是,STM32 的内部上拉是一种“弱上拉”,这样的上拉电流很弱(因为阻值很大,电压较小),如果有要求大电流还是得外部上拉。

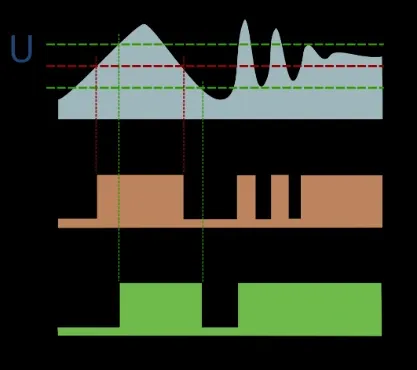

- 施密特触发器:其功能描述为:当输入电压高于正向阈值电压,输出为高;当输入电压低于负向阈值电压,输出为低;当输入在正负向阈值电压之间。具体作用就是用于波形整形,使输入信号具备一定的抗干扰能力(如图)

- P/N-MOS管:关于P/N-MOS管的工作原理,参见26.2.11 ADD [结构基础/数电基础] MOS管、与或非门结构解释,其在此处的作用见后。

2.2 GPIO的工作模式

GPIO共有两组四个共八种工作模式,第一组输入:输入浮空,输入上拉,输入下拉,模拟功能;第二组输出:开漏输出,推挽输出,开漏式复用功能,推挽式复用功能。下面一一介绍:

输入部分

- 输入浮空:上拉/下拉电阻为断开状态,施密特触发器打开,输出被禁止。

这里的浮空包括后面的上拉下拉都是针对上下拉电阻,当两个电阻都处于断开状态时描述为浮空。此时I/O口的电平水平完全取决于外部电路,外部电路输入高电平则为高电平,输入低电平则为低电平。 - 输入上拉:上拉电阻导通,施密特触发器打开,输出被禁止。上拉电阻导通,输入默认呈现高电平并为外部电路节省一个电阻,但上拉电阻阻值较大,电流很小,为“弱上拉”,不适合做电流型驱动。

- 输入下拉:下拉电阻导通,施密特触发器打开,输出被禁止。下拉电阻导通,输入默认呈现低电平并为外部电路节省一个电阻,但下拉电阻阻值较大,电流很小,不适合做电流型驱动。

- 模拟功能:上下拉电阻断开,施密特触发器关闭,双 MOS 管也关闭。该模式用于 ADC 采集或者 DAC 输出,或者低功耗下省电。

输出部分

- 开漏(Open Drain)输出:(1)P-MOS 被“输出控制”控制在截止状态,因此 IO 的状态取决于 N-MOS 的导通状况。(2)只有N-MOS还受控制于输出寄存器,“输出控制器”对输入信号进行了逻辑非的操作。(3)IO 到输入电路的采样电路仍被打开,且可以选择是否使用上下拉电阻。

简单来说,开漏模式下P-MOS管的栅极始终接着高电平而截止,只有N-MOS管能在内部信号输出0再经逻辑非操作变为1后导通 $V_{SS}$ 进而向外部输出低电平。若内部信号输出1,经逻辑非操作后变为1使得N-MOS管截止,使得I/O引脚呈现高阻态(近乎断路的状态),此时若要使I/O输出高电平就必须接通上拉电阻,该上拉电阻可以是内部的也可以是外部(需要大电流驱动时)的。

此外,上拉电阻具有线与特性,即如果有很多开漏模式的引脚连在一起的时候,只有当所有引脚都输出高阻态,电平才为 1,只要有其中一个为低电平时,就等于接地,使得整条线路都为低电平 0。我们的 IIC 通信(IIC_SDA)就用到这个原理。

另外在开漏输出模式下,施密特触发器是打开的,所以 IO 口引脚的电平状态会被采集到输入数据寄存器中,如果对输入数据寄存器进行读访问可以得到 IO 口的状态。也就是说开漏输出模式下,我们可以对 IO 口进行读数据。

- 推挽(Push Pull)输出:此时P-MOS管也直接接入非门,当有信号输入时会传导到两个MOS管,具体表现为:

当输出信号为0时,经逻辑非后变为1,P-MOS管截止,N-MOS管接通,实际输出信号为0;当输入信号为1时,经逻辑非后变为0,P_MOS管接通,N-MOS管截止,实际输出信号为1(高电流)。

上面的描述可以知道,推挽输出模式下,P-MOS 管和 N-MOS 管同一时间只能有一个 MOS管是导通的。当引脚高低电平切换时,两个管子轮流导通,一个负责灌电流,一个负责拉电流,使其负载能力和开关速度都有很大的提高。

另外在推挽输出模式下,施密特触发器也是打开的,我们可以读取 IO 口的电平状态。

由于推挽输出模式输出高电平时,是直接连接 VDD ,所以驱动能力较强,可以做电流型驱动,驱动电流最大可达 25mA。该模式也是最常用的输出模式。

- 开漏式复用功能和推挽式复用功能:此时寄存器输入将不可用,只能通过复用功能输出进行操作。

另外在开漏式复用功能模式下,施密特触发器也是打开的,我们可以读取 IO 口的电平状态,同时外设可以读取 IO 口的信息。

3 结语

我是结语。