26.2.11 ADD [结构基础/数电基础] MOS管、与或非门结构解释

因为看不懂单片机芯片结构在讲什么,又跑去看了看计算机组成原理课程,结果和单片机相关的就搞清楚了两个——总线和储存器储存方式(因为看单片机这两个不知所云),反倒是对数电的逻辑门很感兴趣,一直不知道在具体的实现逻辑上是什么样的。

这里先简单过一下总线和储存器的两个存储方式:

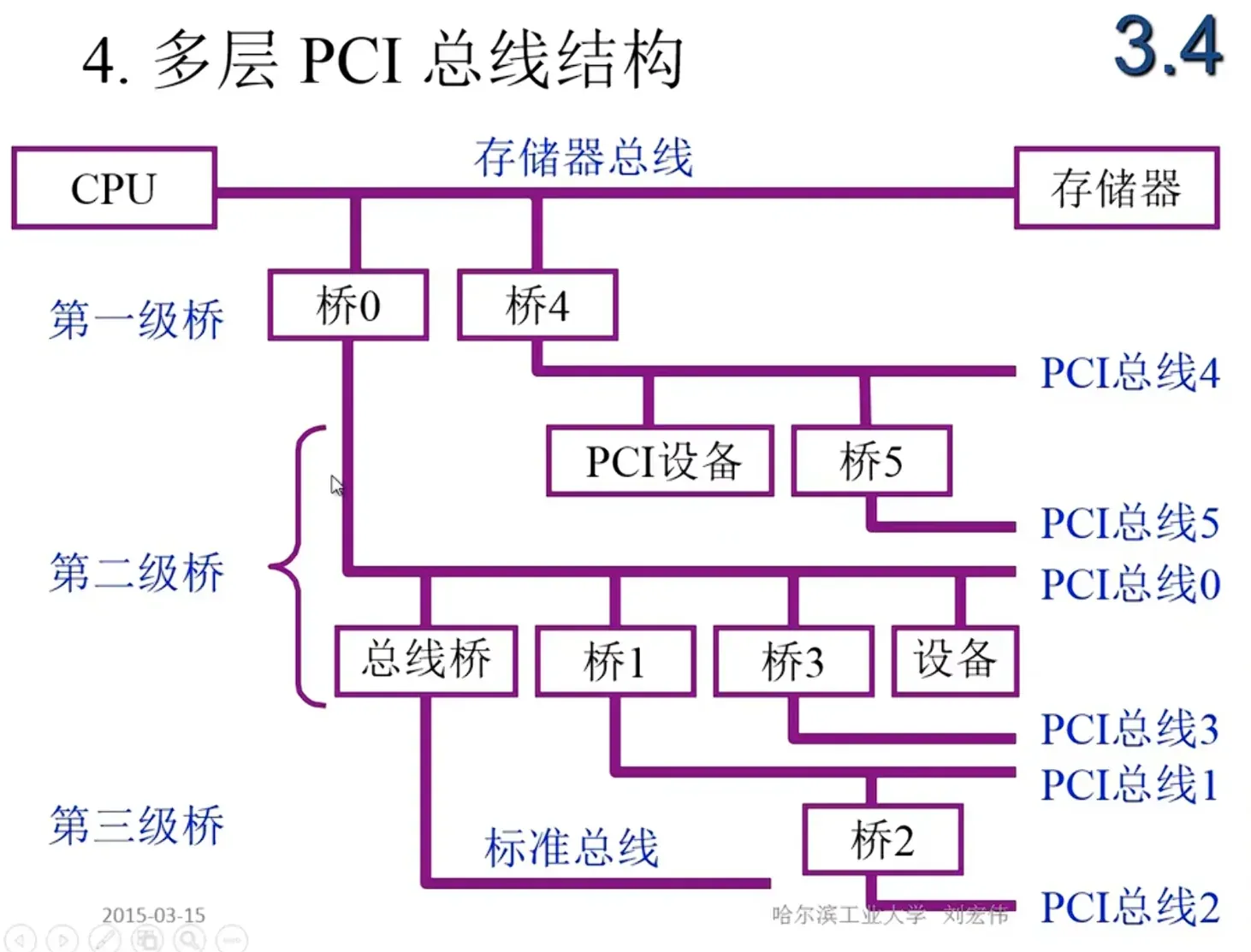

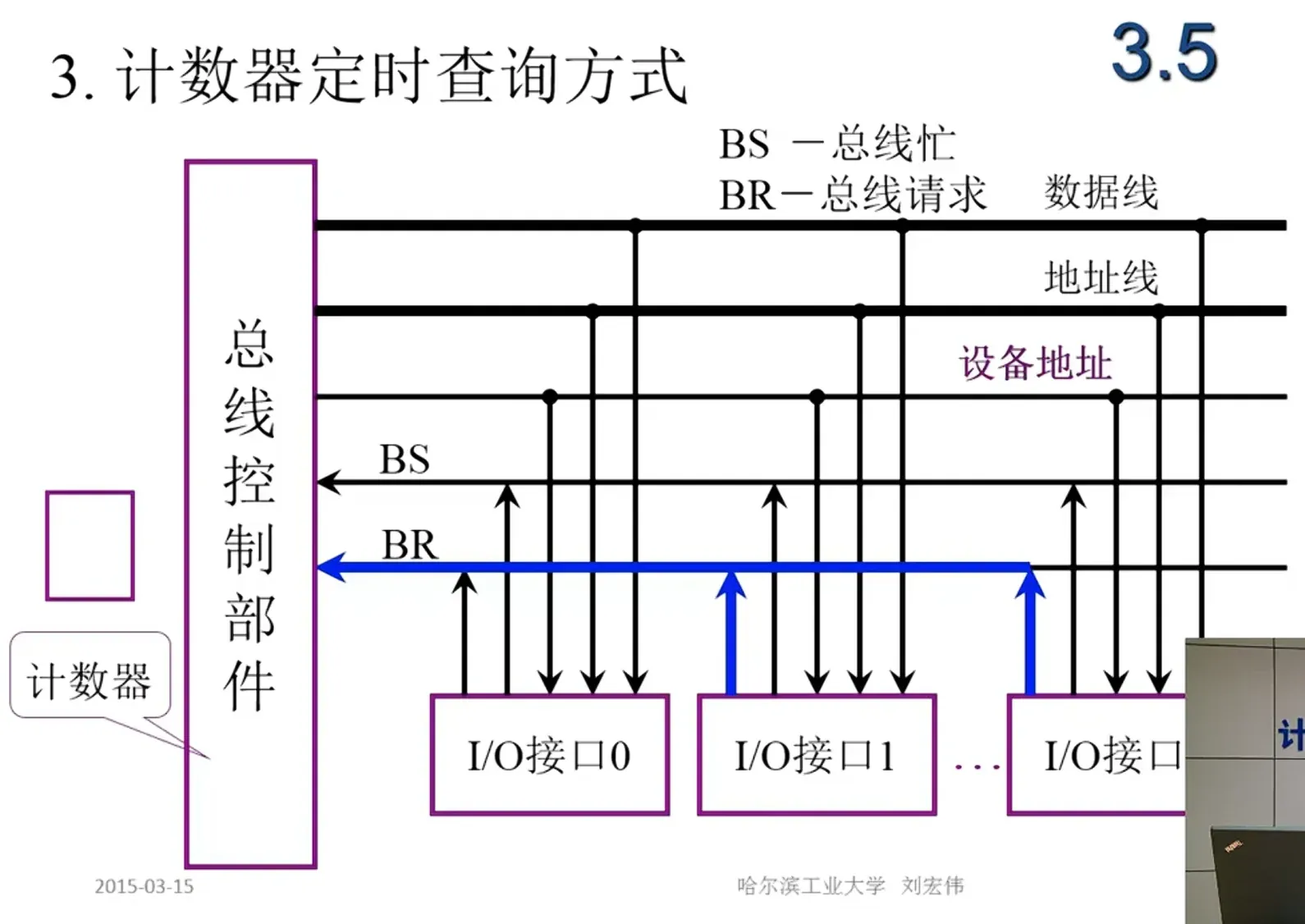

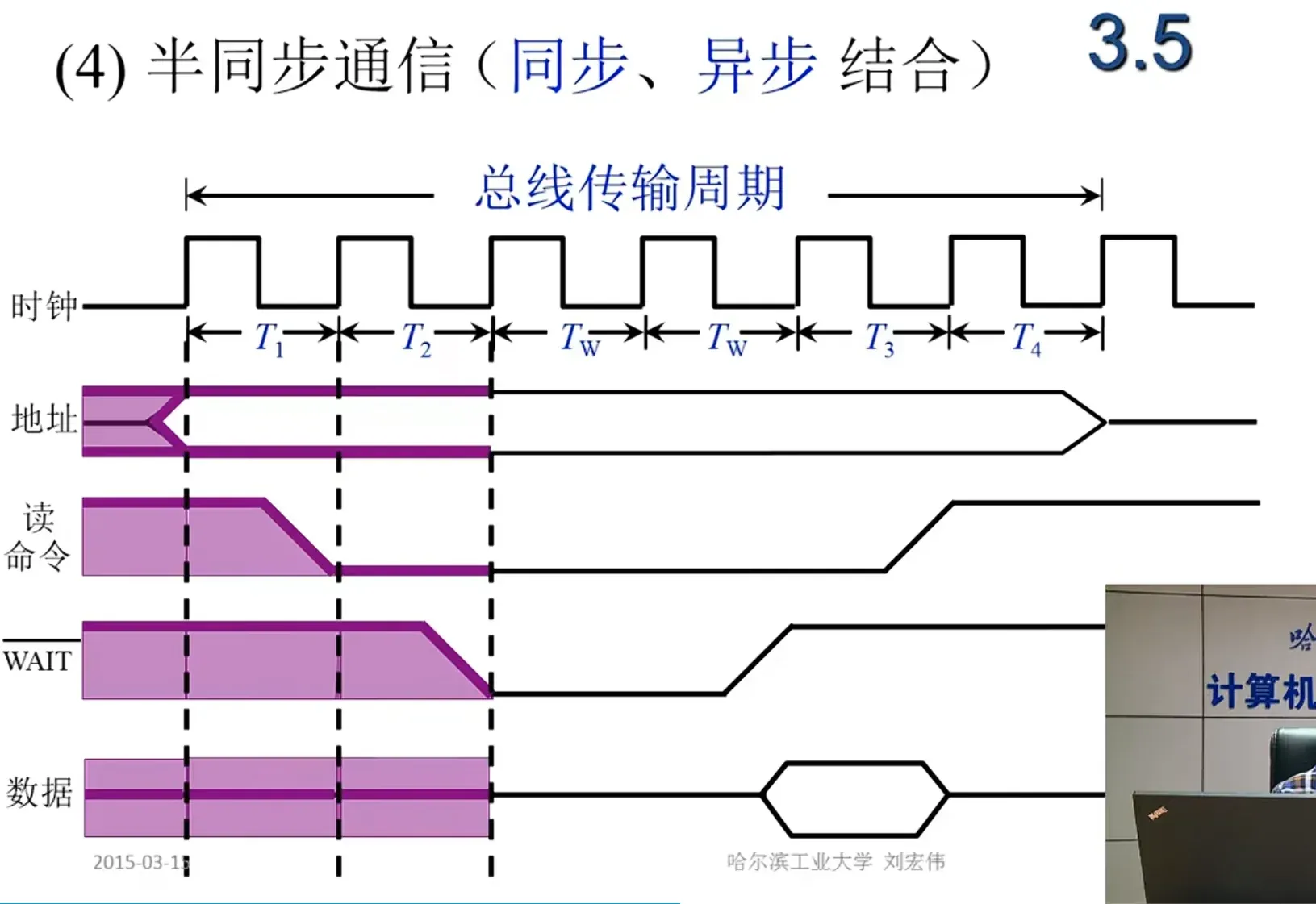

总线,即链接各个部件的信息传输线,相当于主干道。信息在总线上传输方式有两种:串行和并行,并行依赖多根数据线实现。总线可以是各个主设备如CPU、I/O设备、储存器间的链接也可以是次一级设备如辅储存器、拓展设备间的链接。各个总线通过桥进行连接,由此可以得到最复杂的多层PCI总线结构。此外总线被一个设备占用后,其他设备都不能再占用,因此要通过总线控制结构来完成多设备间的信息传递,主要依靠时钟周期实现,具体内容日后再学。

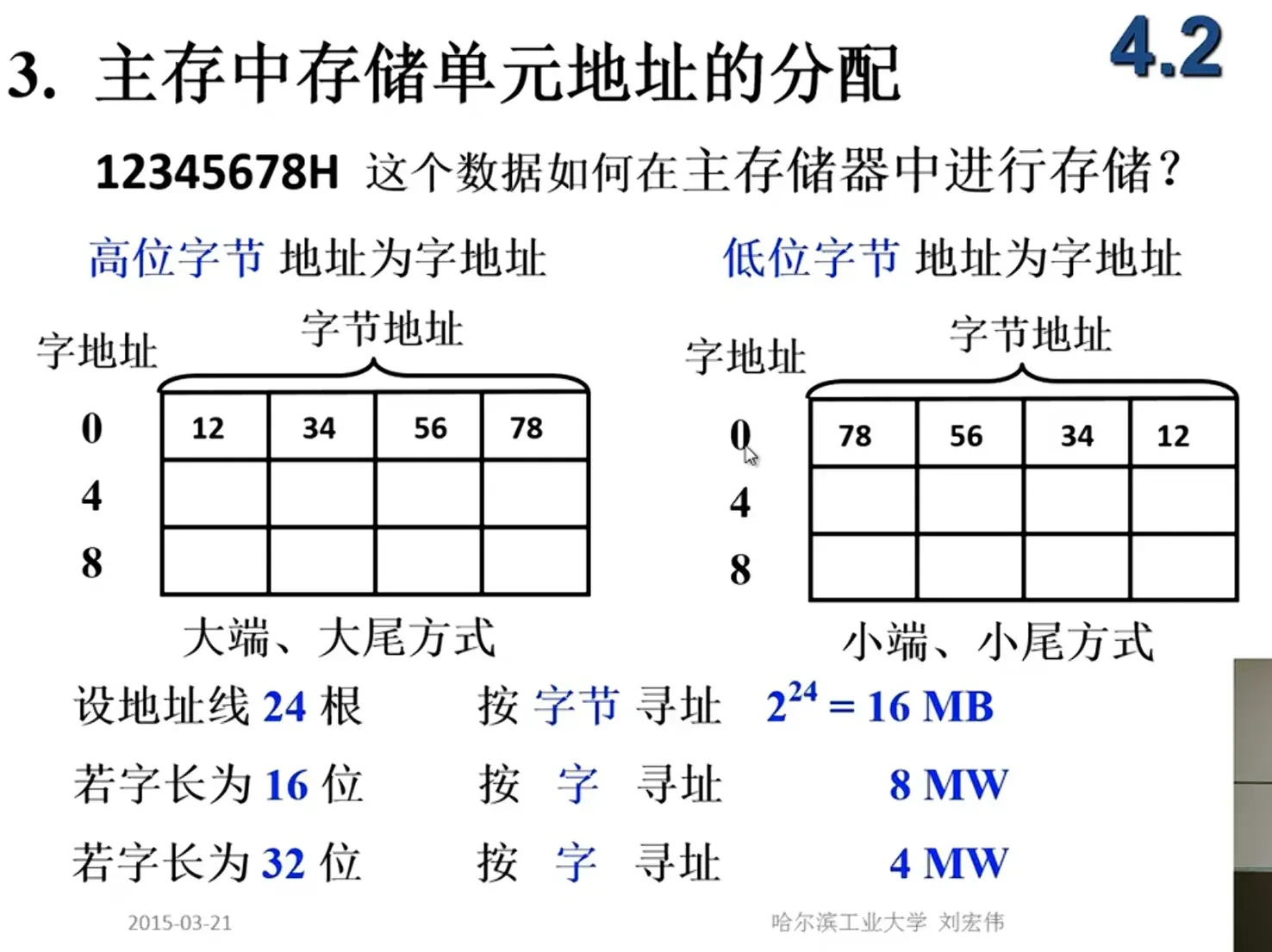

储存器的两个储存方式:即大端/大尾和小端/小尾,指的是数据在地址空间的排序方式,大尾方式即越靠后的数据分配的越大的数据地址上,小尾则反之。一般情况下一个地址空间储存一个字节数据,即256bit,对应的可以储存两位16进制数字,在读取数据时根据不同的存储方式来读取数据,不同存储方式的芯片间不能直接通信。

那么下面开始进入数电。

MOS管:先看视频 另类方式讲解晶体管,让你真正理解,MOS管到底是如何工作的?

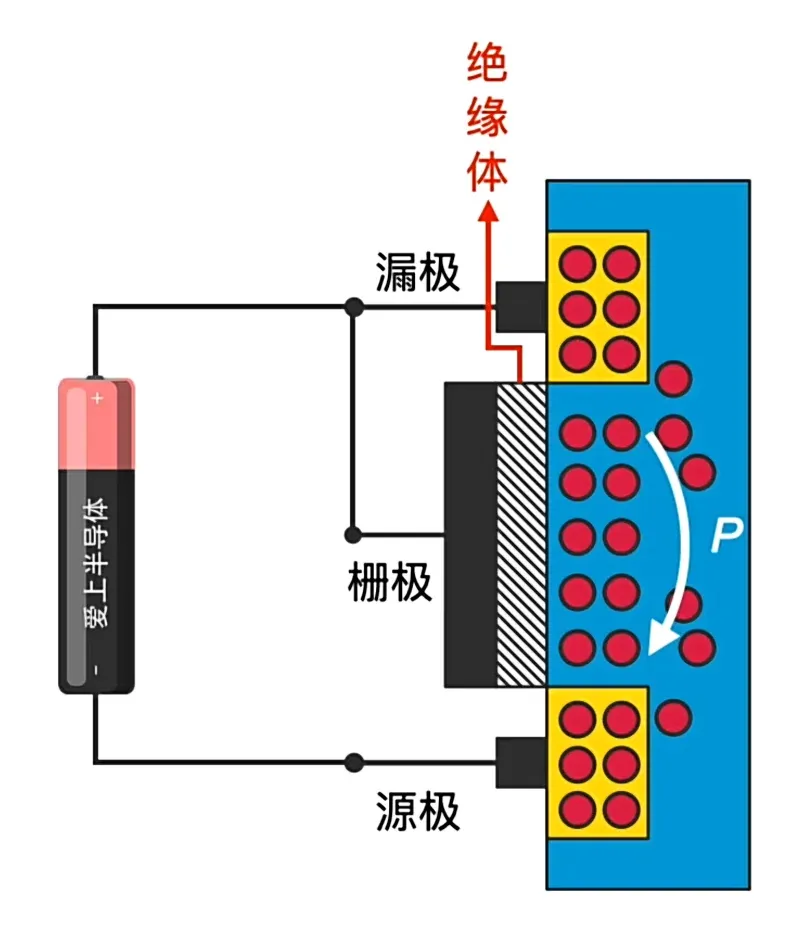

首先MOS管的基础是两种半导体:N(Negative)型半导体和P(Positive)型半导体,其实现原理是在硅(最外层带四个电子,呈稳定结构)中掺杂磷P(最外层带五个电子)或硼(最外层带三个电子)来实现电子的加减。通过半导体的组合加以栅极、漏极、源极的链接来实现一定条件下的联通。

电子加减的目的是使得电子能在电场力的作用下向不同半导体移动,具体见下图

由此就实现了NMOS管栅极给高电平就导通源极漏极,PMOS管栅极给低电平导通源极漏极。那么下面就可以进入与或非的原理实现了

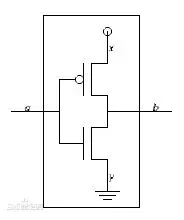

非门:最基础的结构,输出与输入相反的结果,即输入1输出0,输入低电平输出高电平,其实现原理如下:

当栅极输入高电平时,上方PMOS管断开,下方NMOS管联通,输出线接地,显低电平;当栅极输入低电平时,上方PMOS管联通,下方NMOS管断开,输出线接VDD,显高电平。由此实现了非门逻辑。

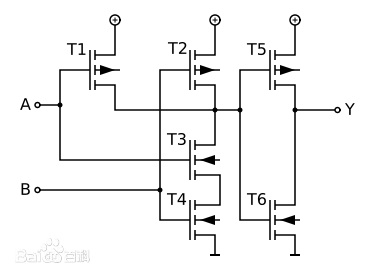

与门:输出 乘 结果的电路(二进制中1×1=1,1×0=0,0×0=0),有两个输入口,只有都输入高电平时才会输出高电平,否则均为低电平,其实现原理如下:

与门的实现实际上是与非门加与门的组合,如图,其最右边的部分即为非门,此时我们只看左边剩余部分,当A输入高电平时(后续用1/0代替高低电平),T1断开,T3联通,此时B若输入1,T2断开,T4联通,此时T1上方电源无法导通,T2上方电源无法导通,左部分输出为0,经非门反转后输出1。余下情况可逐一实验。

其主要逻辑是一个输入口接入一个完整的非门,并接入到输出口,另一个输入口接入非门并插入到第一个输入口的NMOS管处,在第二个输入口输入1的情况下,第一个输入口形成完整的非门,其输入1时输出0,经右侧非门反转后输出1,输入0反之;在第二个输入口输入0的情况下,其上方的PMOS管直接联通VDD输入高电平,再经非门完成反转,最终输出0。

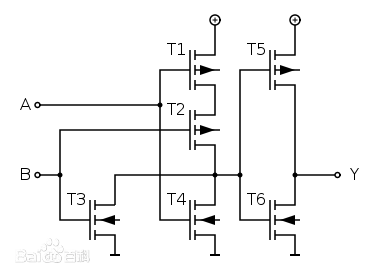

或门:实现逻辑加的电路(二进制中0+0=0,1+0=1,1+1=10(进位取1)),有两个输入口,只要输入高电平就会输出高电平,其实现原理如下:

把非门部分去掉我们可以发现或门其实就是将与门中的VDD接法换成了GND,按照与门的逻辑再推一遍:当A输入0时,B形成完整的非门,并与输出口连接,此时B输入1,左部分输出0,经非门后输出1,输入0反之;当A输入1时,B非门失去VDD电源供应,输出口接地,输出0,经非门后输出1

通过这三种基本逻辑电路,加上移位寄存器就能实现加减乘除,具体实现方法日后再学,数学计算方法见:二进制算术运算 || 补码 || 数电

26.2.19 ADD 电磁铁实现逻辑门:用电磁继电器实现逻辑门

看得我头痛